Cadence University Program

Welcome to the home page of the Cadence Users Group at Cal Poly Pomona. Students obtain practical experience in advanced electronics design using state-of-the-art CAD tools, computing and laboratory facilities.

Cadence products used in classes in the ECE Department

- ECE 109/L- Intr. to Electrical Engineering/Lab

- ECE 207/L- Network Analysis I /Lab

- ECE 209/L- Network Analysis II /Lab

- ECE220/L Electronic Devices and Circuits /Lab

- ECE 307/L- Network Analysis III /Lab

- ECE325/L - Electronic Design of Digital Circuits /Lab

- ECE 405/L- Communication Systems /Lab

- ECE 415/L - Digital Design using Verilog /Lab

- ECE 424L - State Machine Desing using VHDL Lab

- ECE 418 - Integrated Circuit: Design & Fabrication

- ECE 423 - VLSI Circuit Design

- ECE 400 - Special Problems - NASA PAIR Team Project

- EGR 481/EGR 482 - Senior Project Design /Lab

- EGR 558 - Computer Arithmetic

- EGR 594 - FPGA Design Lab

- EGR 691/692 - Master's Project

Cadence products used in research in the ECE Department

- Dr. Brita Olson - Camera on a chip

- Dr. Yi Cheng - Computer Vision

- Dr. Yi Cheng - Hardware/Software Co-Design

- Dr. Yi Cheng & Dr. Meng-Lai Yin - DNA Sequence Matching

- Dr. Halima El Naga

- Dr. Saeed Monemi

- Dr. Rajan Chandra

- Dr. Toma Sacco

- Pspice tutorials (By Dr. Olson)

- Prof Frank Smith uses PSpice in his ECE 109 Lab

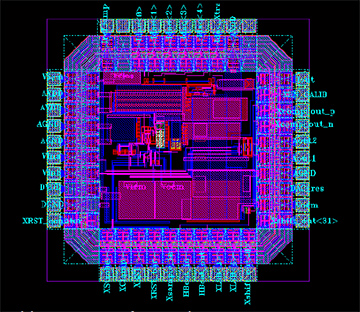

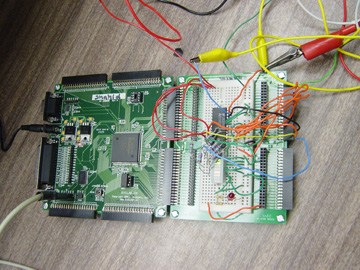

- Picture of Camera System-on-a-Chip designed by undergraduates for their Senior Project

- Undergraduate system-on-a-chip projects

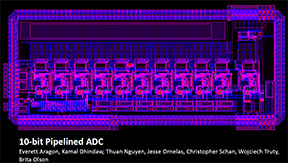

Test chip containing CTIA, current reference and comparator

By: Iain Chalmers, Anthony Drake, LiChun Huang, Alexander McKee, Charles Ritenour, Ron Salloum

Advisor: Brita Olson

See also Cadence at CMOSedu and Tutorials.

Cadence is a registered trademark of Cadence Design Systems, Inc.

2655 Seely Avenue, San Jose, CA , 95134

Phone: 408.943.1234

Fax: 408.428.5001

Responsible party for the site: prnelson@cpp.edu

Electrical & Computer Engineering Department

Date last updated: February 6, 2017